HBM內存、CoWoS封裝的國產化替代思考:一個字 難!

隨著生成式人工智能(AI)的持續火爆,市場對于高性能AI芯片的需求,也帶動了此類AI芯片內部所集成的高帶寬內存(HBM)的需求爆發。

根據市場研究機構Gartner的預測,2023年全球HBM營收規模約為20.05億美元,預計到2025年將翻倍成長至49.76億美元,增長率高達148.2%。

作為HBM市場的領導廠商,SK海力士最新公布的2023年財報也顯示,受益于AI市場的需求,其HBM3的營收較2022年增長了5倍以上。

去年年底,韓國媒體還曾爆料稱,已分別向SK海力士和美光預付了7000億至1萬億韓元的預付款,用于訂購大量 HBM3e內存,為其 AI 領域的下一代產品做準備。

不久前美光CEO Mehrotra也曾指出,其專為AI、超級計算機設計的HBM3E預計2024年初量產,有望于2024會計年度創造數億美元的營收。Mehrotra還對分析師表示,“2024年1~12月,美光HBM預估全數售罄”。

目前HBM市場的供應商只有SK海力士、三星、美光三家,且產能都比較有限。

數據顯示,在2022年HBM市場中,SK海力士占據50%的市場份額,三星占比40%,美光占比10%。

而HBM產能供應上的瓶頸,也與CoWos封裝產能瓶頸有關,這也同樣是英偉達(NVIDIA)等的AI芯片的供應瓶頸。

一、HBM難在哪?

HBM全稱為High Bandwidth Memory,即高帶寬內存,與常規的DDR DRAM不同,HBM是將很多個DDR DRAM芯片堆疊在一起,然后與GPU/GPU封裝在一起,實現大容量、高帶寬、低延遲的DDR DRAM組合陣列。

如下圖,HBM是將多個DRAM堆疊在一起,Die之間通過TVS硅通孔和Microbump連接。DRAM下面是則是DRAM邏輯控制單元, 對DRAM進行控制。

CPU/GPU和DRAM堆棧通過uBump和Interposer(起互聯功能的硅片)連通。Interposer再通過Bump和 Substrate(封裝基板)連通到BALL。最后BGA BALL 連接到PCB上。

正如前面所說,HBM可以帶來大容量、高帶寬、低時延、占用面積小等優點,但是同樣也面臨著技術難度高、良率、高成本、散熱等方面的問題。

比如,HBM依賴昂貴的硅中介層和 TSV工藝來制造,并且HBM 的 2.5D 結構會產生熱量,而靠近 CPU 和 GPU 的布局又會加劇這種情況。

另外,HBM走線長度短、焊盤數高,在PCB甚至封裝基板上無法實現密集且短的連接,因此還需要CoWoS等2.5D先進封裝技術來實現。

CoWoS能以合理的成本提供更高的互連密度和更大的封裝尺寸,目前大部分HBM均使用的此項技術。

因此,無論是對于HBM來說,還是對于高性能的AI GPU來說,他們的產能都將受制于CoWoS產能。那么2024年,HBM的代工產能情況如何?國內是否有國產化HBM及其封裝工藝的替代?

近日,知乎答主@Morris.Zhang 發文對此進行了分析:

二、HBM芯片的代工產能測算

@Morris.Zhang 認為,2024年SK海力士、美光、三星這三家的HBM產能會擴產到75萬片/年,以12層的HBM3e當前良率90%計算,約可切出750顆/wafer,即2024年全球總計能夠產出超過5600萬顆的HBM產能(12層 + 8層),上半年產能比例略小;12層HBM顆粒的渠道單價測算是$250+/顆,那么此前傳聞的英偉達斥資約13億美元預定的HBM訂單,僅能預定520萬顆,僅占2024年總產能的小部分。

補充說明:12層HBM顆粒的渠道單價測算$250+/顆,價格相比一年前略有上浮;換一個測算角度:目前在AI-HPC計算芯片上,通常6顆容量16GB的HBM3顆粒的合計成本約$1500+,相當于$15.6/GB;換算到H100 SXM5,6顆HBM3 80GB,相當于$18.75/GB,約占芯片物料成本的50%+。

倘若基于2024年CoWoS產能來算:

英偉達預定了至少約14+萬片wafer(包含臺積電12萬片以及作為第二供應商的Amkor 2-3萬片產能,后者良率較低),設想平均38%良率切出450+萬顆GPU,那么每GPU搭配6片顆粒,即需要至少2700+萬顆HBM,意味著英偉達僅采購HBM都需要花費68億美元。

倘若按照2024年全球的GPU+HBM組合的產能來算:

截至Y24-Q4,各家CoWoS GPU產品的預定產能大約900萬顆,結合明年三家HBM原廠的擴產計劃總計近6000萬顆HBM(12層為主,8層略少);這兩份供應數據就是吻合的。同時也說明2024年的CoWoS和HBM產能都是充足的。

不過雖然產能不缺,但是上述數據畢竟是“年度計”,很多產能直到Y24-Q4才會開出,而各家預定的產能當然是越早越好,時效性是關鍵條件,上半年初的機會窗口更重要,倘若下半年才開始投產,黃花菜就涼了。

注釋 1:上述談到的CoWoS全球封裝產能是估算約30萬片wafer,包括臺積電27萬片 + 安靠4萬片(估算晶圓數據約有1萬誤差,且后者作為second source的Amkor良率很低);

以及,這些晶圓流片的工藝節點都集中在5nm和3nm,因此yield%保守平均估計在最高38%,約切出900萬顆GPU die;每顆GPU搭載6片HBM顆粒是假定最小配置,如AMD MI300 GPU是搭配8片HBM顆粒。則2024年全球的HBM顆粒總需求估算為5500萬顆(12層為主)。

諸如英偉達RTX系列使用GDDR6顆粒的消費卡,不會算入CoWoS產能;上述的英偉達14萬片wafer是特指Hopper和B100(5nm/3nm),估算2024年英偉達HBM顆粒訂單需求是2700萬顆。

注釋 2:雖說三星也計劃導入全棧CoWoS,但了解到2024年可能開不出產能,2025年可能對三星更有利,作為同時供應HBM和CoWoS的IDM,工藝特點和價格優勢是顯見的。

其次,諸如UMC和GlobalFoundries等產線也可以做前道65nm interposer(但是這兩家的工藝節點微縮到14nm就停止了,沒有先進制程),因此即不能代工前道的先進工藝logic和interposer,也不能完成一條龍的CoWoS全棧。

另外,倘若Y25 INTC IFS 獨立運營,其封裝方案也值得觀望。

三、HBM及其封裝工藝的國產替代

- HBM存儲顆粒的國產化

H100芯片的物料成本保守測算在$3300+,其中50%-60%都是HBM3(6顆粒),80GB容量花費的單位成本相當于$18.75/GB;除了Logic Area之外的其它物料(晶圓、封裝前后、基板等物料)都是標準定價。

當前我們看到HBM全球庫存和渠道周轉十分緊張,實際原因是供應商僅有SK Hynix一家,恰逢AI大語言模型趨勢帶來的HBM需求高峰。

2024-2025年,三星、美光的HBM產能都會陸續開出,各廠提前預訂產能,渠道也會隨之松弛下來,屆時甚至現貨市場的HBM顆粒都可以直接采購,演變成DRAM現貨渠道的業態。

但是談到國產化,韓美三家內存廠的HBM是否可以供應給國內?

該問題要從“三個方式”來看:

一則三家內存廠不會直接走ToB集成合同供貨給國內客戶,特別是某些受限的企業;

二則國內廠商可以直接從現貨渠道采購HBM顆粒,進而再適配控制器、適配I/O和邏輯封裝;

三則國內廠商可以直接從現貨渠道采購DRAM顆粒,進而再通過封裝工藝堆疊成HBM,再適配控制器、適配I/O和邏輯封裝。

針對“第二、第三種方式”做進一步解讀:

第二種方式:單就HBM顆粒而言,目前Hynix HBM的產能緊張是出于供需失衡,而非出于政策限制。

因為,存儲顆粒是一種標準品SKU,無需針對顆粒本身做客戶化定制,于是這個品類就產生了所謂現貨市場。

標準現貨是可以通過渠道或分銷平臺正常流通的,即倘若2024年三家內存廠的產能開出,則全球各區域的代理商庫存都會充足,無數的次級渠道/次級代理商都可以無限轉售;因此,只要現貨庫存充足、價格趨勢向好,現貨市場便永遠可以拿貨,這是內存顆粒的產業特性。

因此,倘若某些受限的國內廠商需要HBM,而不能獲得SK海力士的合同供貨和集成定制,則可以從現貨市場采購,其它國內廠商也可以效仿,即直接從現貨渠道采購HBM顆粒,進而再適配控制器、適配I/O和邏輯封裝。

推測昇騰搭載的HBM就是現貨渠道采購的HBM或2D-DRAM顆粒,重新堆疊封裝后的產物(采購2D-DRAM再堆疊封裝的方式屬于“第三種方式”)。

第三種方式:相比第三種方式更多一道工序,即堆疊封裝,需要攻克幾個技術課題。國內有1-2家專業廠商可以從事這種工作:通過從現貨市場采購2D-DRAM顆粒,再通過TSV垂直方向通孔、Hybrid Bonding鍵合的封裝工藝實現堆疊出一個HBM器件。

需要指出的是,2023年下半年,佰維存儲在東莞松山湖高新區落地了一套封裝產線“晶圓級先進封測制造項目”,該廠區項目的另一個實施主體是“芯成漢奇半導體”(佰維持股70%),項目主題是通過TSV和混合鍵合工藝實現針對DRAM顆粒的多層堆疊封裝,甚至是異質集成。

假以時日,該廠應該可以穩定供應國內部分廠商的HBM需求,甚至搭建起國內封裝的HBM現貨渠道和合同定制服務,推測初代產品可能會在較高的線寬節點堆疊(同時受限于interposer和CoWoS),顆粒密度小一些,頻率/位寬/帶寬規格小一些,但未來可期。

還有第四種方式:自主研發HBM顆粒和器件。

國內希望拿到三家HBM內存原廠的HBM合同供貨和集成定制,但是受到BIS禁令限制;那么除了上述兩種方式獲得HBM內存,還可以寄希望于自研產品。

國內廠商SwaySure、長鑫都在自主研發HBM,前者進度更快。二者都有來自臺灣的研發高管,DRAM顆粒沒問題,但目前沒有產品化的SKU,HBM則可能要期待2025年或更長時間。

內存/顯存作為核心計算設備,它的自研不是由存儲廠商獨立完成,需要“現代計算Hierarchy的各層廠商”全部參與其中,成熟的通用主存/顯存器件需要適配主板PCB和主芯片,還有控制器、協議、底層PHY的搭配設計都很重要,因此HBM基本是與主芯片廠商同步做研發和集成的。

另外,從封裝工藝角度,產業化HBM的另一個阻礙在于封裝,受限于interposer和CoWoS。

- CoW+WoS封裝的國產化

參考GPU芯片構型,倘若缺少CoWoS封裝結構,HBM都無處擺放。

目前全球可選的CoWoS產能供應商有幾個類別:

其一是臺積電的CoWoS;

其二是由臺積電完成晶圓和前道interposer的制造(即CoWoS的“CoW”部分,堆疊+互連),隨后交由自家封裝廠(例如空閑的InFO產能)或是合作第三方OSAT封裝廠完成“on Substrate”部分,即封裝在基板上;

其三是可委托由UMC/GF生產interposer,隨后再送交Amkor或日月光等OSAT產線,委托完成“WoS”部分;

其四是三星I-Cube/H-Cube和Intel Foveros,兩家都可以完成全棧CoWoS交付;

其五是國內也有一部分CoWoS的能力,但幾乎全部是CoW+WoS的工藝對接。

諸如UMC和GlobalFoundries等產線可以完成CoW部分的制造,即前道interposer,工藝節點基本在65nm(這兩家的工藝節點微縮到14nm就停止了,沒有先進制程);因此這類廠商即不能代工前道的先進工藝logic和interposer,也不能完成一條龍的CoWoS全棧。

能夠獨立完成較高工藝節點、較高良率的全棧CoWoS的廠商,唯有TSMC/Samsung/INTC。

對于國產化的CoWoS封裝廠商,盛合晶微和通富微電都有從事Chiplet封裝,兼顧包括前道interposer的生產。

通富微電也在國內和海外分別設有廠區;此前傳聞稱AMD MI300 CoWoS的封裝代工會委托給通富微電,但隨后證實是誤傳,實際情況是:AMD曾計劃將封裝的bumping工序委托給通富微電(檳城工廠),但最終沒有合作;通富微電主要是服務于國內。盛合晶微和通富微目前還存在一些良率缺陷,拉動良率是一個緩慢的過程。

其實相比其它制造工序而言,CoWoS并沒有極度前沿的技術門檻,唯一的關節是它要保證在高微縮制程下的高良率,因為在封裝層面,倘若出品有較高的不良/失效,那么上面堆疊連接的HBM等等器件就變成無可挽回的損耗了;通過兼顧較高工藝節點和良率的,目前唯有臺積電。單就CoW+Wos產能而言,全球可以開出很多產能(尤其WoS廠商),但是能夠適用于先進計算芯片的工藝/良率的產能則并不多。

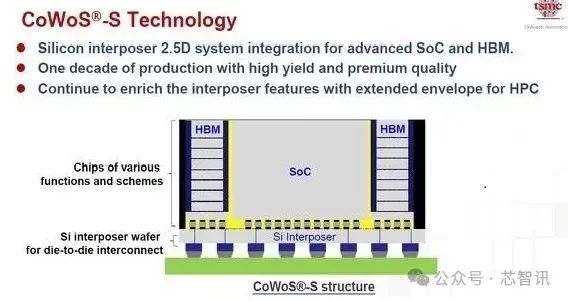

出于微縮IC面積,CoWoS的方法就是在Substrate上面增加一層Si interposer,芯片依然通過覆晶方式正面朝下連接在這個中介層上;它就承擔die-die互連以及die-substrate互連。

由于interposer是按芯片工藝制造(如初代的65nm),其布線密度可以非常細密(初代<10um),die-die之間也可以堆疊更緊密。

導致上述良率門檻的原因是工藝:以WoS良率為例,難點主要在于其封裝的中介層尺寸應當有嚴格限制,即Si interposer面積需要大于其上面2個甚至多個die的尺寸之和。

然而隨著這個尺寸越來越大,CoWoS-5甚至通過一種"2-way lithography stitching approach技術"使得interposer尺寸可以擴到2500nm2(接近3x reticle limit,6代CoWoS尺寸甚至接近4x reticle limit),那么隨之帶來的工藝風險就是,on wafer邊緣的扭曲、接角的垂直凸變問題就會發生,導致封測后不良。而TSMC CoWoS工藝磨合了10幾年,積累大量knowhow,才獲得如今可靠的高良率。

對于OSAT專業封裝廠(包括Amkor/日月光等),導致工藝良率拉升緩慢的因素還有就是與前段interposer的分開制造,雖然CoW+WoS是合理的產業鏈分工,但是拉升兩者共同出品的良率需要兩家工藝同步發展。

國內的interposer基本是由SMIC制造,再將其委托給OSAT專業封裝廠完成WoS封測;而倘若不能獲得SMIC interposer制造,也可以委托UMC/GF代工。

如今,SMIC interposer雖然做不到3nm,但可以使用7nm代替;而且SMIC的先進封裝工序也是獨立出來,成立子公司運行。

能夠獨立完成較高工藝節點、較高良率的一條龍全棧CoWoS的廠商,唯有臺積電、三星、Intel(Logic die+interposer+CoWoS)。

未來的趨勢,可能全球大部分2.5D封裝都會是前道-后道合作的模式;前道Fab提供interposer做CoW,后道有載板的做WoS。另外,CoWoS也會更多下沉適用到其它場景,非移動裝置涉及AI-HPC的未來大部分產品都會依賴CoWoS封裝,2.5D/3D封裝目前來看還是Foundry相比OSAT更具優勢。

本站所有文章、數據、圖片均來自互聯網,一切版權均歸源網站或源作者所有。

如果侵犯了你的權益請來信告知我們刪除。郵箱:business@qudong.com